在设计基于FPGA的电子系统时,一般需要用示波器、逻辑分析仪等外部测试设备进行输入输出信号的测试,借助测试探头把信号送到测试设备上进行观察...SignalTapII就是这样一种嵌入式逻辑分析器(embedded logicanaIyzer)

”SignalTap II,FPGA“ 的搜索结果

在设计基于FPGA的电子系统时,一般需要用示波器、逻辑分析仪等外部测试设备进行输入输出信号的测试,借助测试探头把信号送到测试设备上进行观察...SignalTapII就是这样一种嵌入式逻辑分析器(embedded logicanaIyzer)

FPGA驱动ADS1271的Verilog语言实现

学习fpga的工具signaltap软件使用说明书,好工具

使用SignalTapII调试FPGA中AD采样控制逻辑 精简易懂

SignalTapII使用,在fpga设计调试中很好用的工具

signal tap ii FPGA开发测试模块 Verilog HDL 语言

使用SignalTapII调试FPGA中AD采样控制逻辑 精简易懂 相关下载链接://download.csdn.net/download/ylpj2011/3233524?utm_source=bbsseo

嵌入式逻辑分析仪Signal Tap II在FPGA设计中的应用、电子技术,开发板制作交流

述I2C总线的原理;介绍几种I2C接口芯片的初始化...以AD9883A的初始化为例,重点说明基于FPGA的I2C配置模块,在QuartusII 软件中进行了I2C 总线主从模式下的仿真,并用其内嵌逻辑软分析仪SignalTapII 完成了硬件调试。

)FPGA的资源是有限的。 设计已经占用了可观的资源(%的LE,%的MB),signaltap还要和设计抢占资源。“抢占”在这里是很贴切的,既包括抢占LE、MB,还包括布局资源和布线资源。我把“抢占”造成的影响叫做“测不准...

调试FPGA是一个比较艰巨的任务,设计越是复杂,则在验证设计上所花的时间和金钱就越多。与硬件逻辑分析仪相比,SignalTapII具有成本低廉,使用方便,灵活性大等特点。

FX3作为FPGA核心的Slave完成与PC的通信验证例程。其中引脚需要按照自己的FX3开发板进行配置。默认配置是HSC的ALTERA开发板,EP4CE22F17C8+CYUSB3014。 同步FIFO传输,使用CyConsole验证通过。内附SignalTapII观察...

我选的FPGA是 cycloneII系列的EP2C5,资源比以前的FPGA多了好几倍,还有PLL,内嵌的RAM,可以试试SignalTapII,用内嵌的逻辑分析仪 测试引脚波形,对于FPGA的调试,逻辑分析仪是至关重要的。利用这块板子我完成了...

FPGA的资源是有限的。 riple 设计已经占用了可观的资源(%的LE,%的MB),signaltap还要和设计抢占资源。“抢占”在这里是很贴切的,既包括抢占LE、MB,还包括布局资源和布线资源。我把“抢占”造成的影响叫做“测...

FPGA&ASIC开发流程

标签: fpga开发

本文介绍了基于FPGA技术的DDS波形发生器的原理与设计,并利用SignalTapII嵌入式逻辑分析仪对正弦波、三角波、方波、锯齿波进行仿

FPGA的结构和设计流程

标签: fpga开发

fpga报告

在分析DDR SDRAM基本操作特性的基础上,根据DDR的时序要求,提出了...控制器逻辑的RTL在FPGA板卡上实现,仿真在Modelsim中进行,硬件的验证利用QuartusII的逻辑分析仪(SignaltapII)完成,以保证存储器的读写高效性与可靠性。

提出了基于FPGA和SDRAM的地闪探测单元存储系统的总体设计,介绍了SDRAM控制器设计中的关键问题及解决方案,给出了SDRAM接口硬件电路,详细介绍了SDRAM控制器的核心部分―――时序控制器的状态转换设计,最后给出...

SignalTapII是quartus自带的一个工具,相当于一个内建的示波器,可以在调试时获得实时的信号的波形 。需要结合硬件平台(如FPGA开发板)使用,用于调试和分析。 Modelsim是一款仿真工具,在调试时无法实时获得...

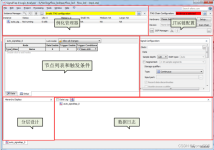

当前signaltapII软件功能的使用基础是在之前led程序上进行的 1 增加需要观察的信号节点 2 添加触发时钟 (这个时钟主要是为了采集这些信息) 3 保存signaltap II 文件到工程目录下 4 再一次...

推荐文章

- Android RIL框架分析-程序员宅基地

- Python编程基础:第六节 math包的基础使用Math Functions_ps math function-程序员宅基地

- canal异常 Could not find first log file name in binary log index file_canal could not find first log file name in binary-程序员宅基地

- 【练习】生成10个1到20之间的不重复的随机数并降序输出-程序员宅基地

- linux系统扩展名大全,Linux系统文件扩展名学习-程序员宅基地

- WPF TabControl 滚动选项卡_wpf 使用tabcontrol如何给切换的页面增加滚动条-程序员宅基地

- Apache Jmeter常用插件下载及安装及软硬件性能指标_jmeter插件下载-程序员宅基地

- SpringBoot 2.X整合Mybatis_springboot2.1.5整合mybatis不需要配置mapper-locations-程序员宅基地

- ios刷android8.0,颤抖吧 iOS, Android 8.0正式发布!-程序员宅基地

- 【halcon】C# halcon 内存暴增_halcon 读二维码占内存-程序员宅基地